High Level Design of Adaptive Real-time Embedded Systems

A Survey

Mouna Ben Said, Yessine Hadj Kacem, Nader Ben Amor and Mohamed Abid

University of Sfax, ENIS, CES Laboratory, Soukra km 3.5, B.P. 1173-3000 Sfax, Tunisia

Keywords:

Adaptation, MDE, UML/MARTE, RTES, Timing Constraints.

Abstract:

Real time embedded systems (RTES) know a growing complexity due to modern applications requirements

and architectures complexity especially with the addition of the multiprocessor feature. They are equally

subject to a variety of constraints due to their mobility. They need to react to environment variability, resource

limitations and timing constraints. An emergent solution to deal with this complexity is the integration of

adaptation strategies in embedded systems design flow. The design space of multi-layer adaptation decisions

is becoming increasingly vast and difficult to explore. Development of such systems at low system levels is

therefore increasingly tedious especially with the limitations of computer aided design tools. Using MDE

approach and the UML/MARTE profile for high abstraction level design is becoming a promising solution

to ease the design of RTES. In the present paper we recall and classify existing works built around adaptive

embedded systems. We concentrate on a set of criteria to help highlighting the shortages of existing approaches

on modern adaptive RTES design. We focus on the design environment, adaptation features, online time

constraints verification and performance assessment. Finally, we present our future works to cope with the

limits of existing solutions while taking into account the observed criteria.

1 INTRODUCTION

Compared to conventional desktop and server sys-

tems, real-time embedded systems are often subject

to numerous constraints due to their mobility. These

include (i) limitations on local resources, imposed by

weight and size constraints, concern for power con-

sumption, and lowered trust and robustness result-

ing from exposure and motion, and (ii) environment

variations such as unpredictable variation of network

load. This makes it impossible to yield an offline opti-

mization. Thus, RTES are asked to dynamically self-

adapt internally to their limited computational and en-

ergy resources as well as to changes in their surround-

ing environment in order to offer the required quality

of service. Self-adaptive systems change their behav-

ior or structure, at run-time, in response to variations

in their execution environmentand according to adap-

tation engine decisions. Researchers have focused on

the integration of adaptation strategies in embedded

systems which further hardens designers’ task. An-

other complexity dimension is added to such systems’

development through their prominent evolution to in-

creasingly complex multiprocessor architectures. In

this way, their design space containing adaptation de-

cisions at different system layers (architecture, appli-

cation, operationg system and network) is becoming

increasingly vast and difficult to explore, especially

with the limitations of computer aided design tools.

Therefore, developing such complex systems using

classic design approaches, which handle technical de-

tails at low system levels, is no more an efficient so-

lution.

There have been numerous contributions in adap-

tation for RTES at both hardware and software (op-

erating system, application) layers. However, there

is a lack of standard formalization of the adaptation

logic that is understandable by everyone, platform-

independent and reusable. At present, there are

great improvements of high level design methods

based on Model Driven Engineering (MDE) method-

ology (Schmidt, 2006) and specifically using the

UML/MARTE (Modeling and Analysis of Real-Time

and Embedded Systems) profile (Group, 2011). Au-

thors in (Gogniat et al., 2010) assert the strong need

for abstraction mechanisms to cope with the limits

of existing design flows and associated tools that are

too tied to hardware platforms and permit designers

to develop more efficient systems. Model based ap-

proachespermit to decrease the complexity of modern

systems using the abstraction mechanism while in-

creasing productivity and reusability and minimizing

341

Ben Said M., Hadj Kacem Y., Ben Amor N. and Abid M..

High Level Design of Adaptive Real-time Embedded Systems - A Survey.

DOI: 10.5220/0004381703410350

In Proceedings of the 1st International Conference on Model-Driven Engineering and Software Development (MODA-2013), pages 341-350

ISBN: 978-989-8565-42-6

Copyright

c

2013 SCITEPRESS (Science and Technology Publications, Lda.)

cost and Time to Market. The MARTE profile permits

to jointly model both hardware and software parts of

RTES which eases the communication between de-

signers and reduces design errors. It allows, as well,

performance and schedulability analysis. However,

existing MDE based adaptation approaches do not

deal with the complete process of adaptation in RTES.

They do not offer, equally, a complete and obvious

support of timing constraints guarantee which is a key

feature in RTES. Additionally, MARTE profile does

not fully support adaptation features for RTES such

as inter-processor tasks migration.

In the present paper, we recall and classify state-

of-the-art approaches around adaptive embedded sys-

tems. While studying these approaches, we concen-

trate on a set of comparison criteria related to de-

sign environment, adaptation process and support of

online temporal and performance analysis. In Sec-

tion 2, we start by defining the considered compari-

son criteria. In section 3, we recall low-level adap-

tation approaches which do not consider a modeling

step. Then, in Section 4, we look through adaptation

approaches based on MDE paradigm. In Section 5,

according to the comparison criteria, we discuss and

compare related works in order to summarize the lim-

its of existing approaches on MDE based design of

adaptive RTES. Then we present our proposed solu-

tion and future works to cope with these limits and al-

low taking the adaptation behavior into account early

in RTES design flow. Finally, we conclude in Section

6.

2 COMPARISON CRITERIA

During our study, we focus on a number of criteria in

which we are interested for our ongoing work. The

first group of criteria relates to the design environ-

ment. We are interested to mention if the approach

is designed at a high level. We are particularly con-

cerned with the UML/MARTE standard which fits our

future works direction (please refer to section 4.1 on

MDE/MARTE). We are also interested in platform

dependency and multiprocessor support criteria. The

second group of criteria is linked to the adaptation

process where we are interested in the modularity of

design and cross-layer adaptation support. We finally

focus on the support of online temporal verification

and performance evaluation.

There is no need to recall the importance and ben-

efits of modularity in complex systems development,

especially in terms of scalability and productivity.

The modular structure of embedded system adapta-

tion process includes:

• Observation: needs to specify resources (ex. CPU

time, network bandwidth or power consumption

observer), trigger events and associated thresh-

olds, and monitoring period.

• Analysis: generates adaptation requests according

to upcoming events. The used analysis test per

constraint has to be defined (such as scheduling

analysis for real time constraint) as well as thresh-

olds to demand adaptation action.

• Decision: needs the specification of a set of adap-

tation strategies and mechanisms, system configu-

rations and selection algorithms to be used to gen-

erate the adaptation solution that best meets the

adaptation requests.

• Action: acts on the system elements to run the

new adaptation solution. It is generally applica-

tion/platform dependent.

• Assessment: required to measure adaptation cost-

effectiveness and make adjustments if needed to

meet the required performances. Metrics have to

be defined, and feedback, estimation and update

techniques need to be settled. Adaptation fre-

quency and granularity, and system stability need

to be considered. Performance models describe

how to measure and interpret application perfor-

mance.

3 LOW-LEVEL ADAPTATION

APPROACHES FOR

EMBEDDED SYSTEMS

There have been numerous contributions to integrate

adaptation strategies in embedded systems develop-

ment process. In the present section, we recall low-

level adaptation approaches in different layers of em-

bedded systems. These approaches do not consider

a modeling step in their development process. We

classify those works in two classes: hardware layer

and software (operating system and application) layer

adaptation.

3.1 Adaptation in the Hardware Layer

We present in the following sub-sections a number

of low-level approaches proposing adaptation tech-

niques which are representative of common state-of-

the-art adaptation techniques.

3.1.1 Power Management Techniques

Portable systems are mostly battery driven and often-

times have to run for considerable time periods. The

MODELSWARD2013-InternationalConferenceonModel-DrivenEngineeringandSoftwareDevelopment

342

most serious limitation on these devices is the avail-

able battery lifetime. Therefore power management

has become a critical issue for those systems. Di-

verse efforts have been made to improve power man-

agement in mobile devices. Dynamic Voltage scaling

(DVS) (Pillai and Shin, 2001) and Dynamic Power

Management (DPM) techniques have been widely

studied as methods for optimizing the power con-

sumption.

3.1.2 Dynamic Hardware Reconfiguration as a

Key Adaptation Feature

Profiting from technological advances, the current

trends show that dynamically reconfigurable architec-

tures are considered a key element in self adaptive

embedded systems development. Researchers in the

domain have focused their works on the development

of new hardware adaptation techniques taking advan-

tage of dynamic and partial reconfiguration (DPR) ca-

pability offered by modern FPGA (e.g. Xilinx de-

vices). The DPR support enables the system to swap

several designs by reconfiguring co-processors or ac-

celerators at run-time. Such feature is beneficial as it

permits to deal with system optimization at run-time

and improve performance. However, it has a nega-

tive effect on surface and energy consumption. So,

to address area, power and performance trade-offs, a

solution is to decide when and how a running appli-

cation has to be accelerated. In (Ye et al., 2010), au-

thors aim at optimizing multi-processor architecture

through HW resources reconfiguration according to

variable applications’ needs in terms of standard func-

tions. In fact, authors have noticed a prominent use

of common standard functions in embedded systems

such as video/image processing and data encryption.

Their approach is based on a reconfigurable MPSoC

architecture model and libraries of hardware and soft-

ware implementations of intensively used standard

functions. They define a reconfiguration decision al-

gorithm which decides at run-time which configura-

tion best fits with application requirements according

to recorded execution time.

3.2 Adaptation in Software Layers

We classify software adaptation in two categories:

adaptation in the OS layer and application-aware

adaptation.

3.2.1 Adaptation in the OS Layer

The role of the OS in an embedded real-time adap-

tive system is to sense external events, monitor and

allocate scarce resources. Generally, OS adaptation

consists in changing resources allocation or modify-

ing the scheduling policy in response to application

and resource variations. In (Vahdat et al., 2000), CPU

resource managers are defined to provide soft real-

time performance guarantees. In (Banachowski and

Brandt, 2002), schedulers adapt the scheduling policy

to handle the variations of application at runtime. K.

Nahrstedt et al. (Yuan and Nahrstedt, 2006; Chu and

Nahrstedt, 1999) have equally dealt with scheduling

policy adaptation. They have proposed in (Yuan and

Nahrstedt, 2006) an energy-efficient soft real-time

CPU scheduler for multimedia applications running

on a mobile device. The EScheduler seeks to mini-

mize the total energy consumed by the device while

meeting multimedia timing requirements. To achieve

this goal, they integrated the DVS into traditional soft

real-time CPU scheduling: it decides at what CPU

speed to execute applications in addition to when to

execute what applications. EScheduler makes these

scheduling decisions based on the probability distri-

bution of cycle demand of multimedia applications

and obtains their demand distribution via online pro-

filing.

An important allocation adapting technique,

which is increasingly used in modern systems with

multiprocessor architecture, is inter-processor tasks

migration (Goossens et al., 2003). It consists in re-

allocating tasks on execution units following a re-

source variation event. The event can be a work-

load variation due to a task entry or exit event in or-

der to respect timing constraints. This is a classic

problem often encountered and extensively studied in

distributed systems such as web servers or local net-

works. It is however not well tackled in embedded

systems especially in the case of heterogeneous mul-

tiprocessor architectures. Different strategies can be

envisaged. The simplest is to execute the most com-

plex tasks on the most efficient processors. The op-

erating system to be used has to manage processors

heterogeneity issue which presents a significant chal-

lenge when the processors have different instruction

sets.

3.2.2 Adaptation in the Application Layer

Modern applications, specifically multimedia ones,

are becoming more and more complex and have in-

creased computational demands that may exceed ex-

isting embedded systems capacity. Application-aware

adaptation is then an important capability of embed-

ded systems that has been largely tackled in the liter-

ature. Application level adaptation techniques have

been essentially developed for multimedia systems

since they fit very well multimedia applications, such

as H264 and JPEG2000 codecs, which are highly

HighLevelDesignofAdaptiveReal-timeEmbeddedSystems-ASurvey

343

configurable. It is hard to conceive a universal al-

gorithm that can perform well for all kinds of con-

tents. However, if important characteristics of ap-

plications can be identified and utilized to trade-off

output quality for resource usage and user prefer-

ences (ex. Trade-off output video quality for net-

work bandwidth availability), one can design an ad-

justable algorithm that can tune its parameters (algo-

rithms or configuration parameters) to adapt to envi-

ronment variations. This tuning technique has been

widely used in literature (Said et al., 2011) (Mesarina

and Turner, 2003) (Ngoc et al., 2002) (Hsia, 2003)

(Satyanarayanan et al., 1995). Mesarina and Y. pro-

posed in (Mesarina and Turner, 2003) a method to

reduce the energy for a specific multimedia applica-

tion, the «decoding MPEG», using parameter modifi-

cations. Authors in (Ngoc et al., 2002) presents a QoS

framework for interactive 3D applications where the

QoS management relies on high-level QoS parame-

ters (e.g. PSNR) of quality scalable 3D objects. This

framework aims at guaranteeing the user specified in-

teractive frame rate through degrading the 3D objects

quality in such a way that minimal overall quality

degradation over the scene is obtained.

3.3 Cross-layer Adaptation

The above adaptation techniques have been shown to

be effective for both QoS provision and energy sav-

ing. However, most of them adapt only a single layer

or two joint layers. More recently, researchers have

proposed cross-layer adaptation frameworks where

different system layers adaptations are coordinated in

order to fully exploit the adaptation benefits (Yuan

et al., 2006) (Vardhan et al., 2009) (Diguet et al.,

2011) (Loukil et al., 2009). Some of these cross-layer

approaches adapt only at coarse time granularity (Pil-

lai et al., 2003)(Mohapatra and Venkatasubramanian,

2003), e.g., when an application joins or leaves the

system. This infrequent adaptation is proven to be

insufficient to deal with small changes in the system

environment and processed data. Then, some other

cross-layer adaptive frameworks have been proposed

to adapt systems at both coarse and fine time granu-

larities. We present hereafter some recent cross-layer

adaptation approaches.

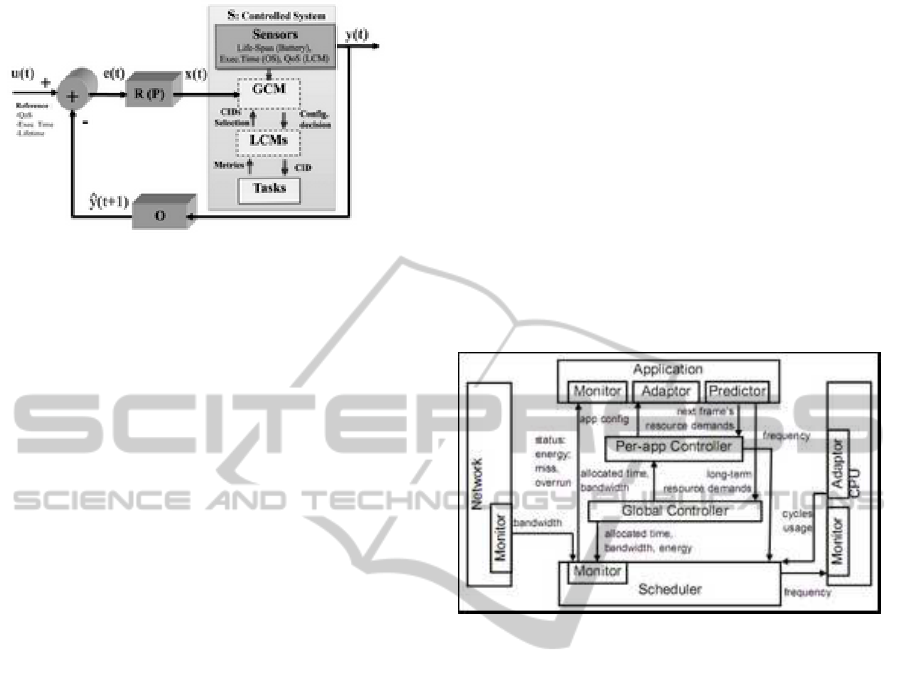

3.3.1 A Closed Loop Adaptation Approach

J. Philippe et al. have presented in (Diguet et al.,

2011) an OS based adaptation approach for reconfig-

urable embedded systems. The main objective of this

work is the implementation of reconfiguration man-

agers with runtime decision and configuration con-

trol capabilities. As illustrated in Figure 1, a hi-

erarchy of local and global configuration managers

(LCM/GCM) is used to permit the separation between

application-specific and application-independentcon-

figuration decisions. Authors have been interested in

both architectural and algorithmic reconfigurations.

The algorithmic reconfiguration is performed by the

LCM which selects an application-specific algorith-

mic configuration independently of implementation

details. However, the architectural reconfiguration is

in charge of the GCM. It consists in tasks migration

from software to hardware on a multiprocessor het-

erogeneous architecture based on a master GPP pro-

cessor, a specific processor and reconfigurable hard-

ware accelerators. Equally, a RTOS is used for trans-

parent execution of tasks with their different HW and

SW implementations, and the reconfiguration engine

has been implemented as new OS services. A con-

figuration table, which is built at an offline design

space exploration step, contains a set of configura-

tions among which one configuration is selected at

run-time. A configuration is a combination of local

and global parameters which correspond to both al-

gorithmic and architectural (HW/SW tasks partition-

ing) configurations. Three constraints are supposed to

be respected in this work: application QoS, execution

time and power consumption. A simple timer, pro-

vided by the RTOS, is used for tasks execution time

monitoring.

In addition to adaptive behavior integration, this

work is one of the few works that were interested

in studying system stability when self-adapting. Au-

thors define a configuration period equals to Ne ap-

plication iterations in order to minimize control and

reconfiguration overhead. Every period, local and

global managers collect metrics, and then the next

configuration is selected so that the required QoS is

respected and power consumption and execution time

are optimized. This work has nearly covered the dif-

ferent steps required in adaptation process but has the

limitation of being developed at a low level which

makes it difficult to handle and requires a high level

of expertise at hardware implementation. In addition,

Target systems run a static set of tasks and reconfigu-

ration decisions are limited to a pre-characterized set

of configurations which does not fit to modern sys-

tems with dynamic tasks set. Furthermore, the prede-

fined configurations have to be permanently loaded on

the chip which increases static power consumption.

Finally, Altera devices, without dynamic reconfigura-

tion capability, were considered in this work.

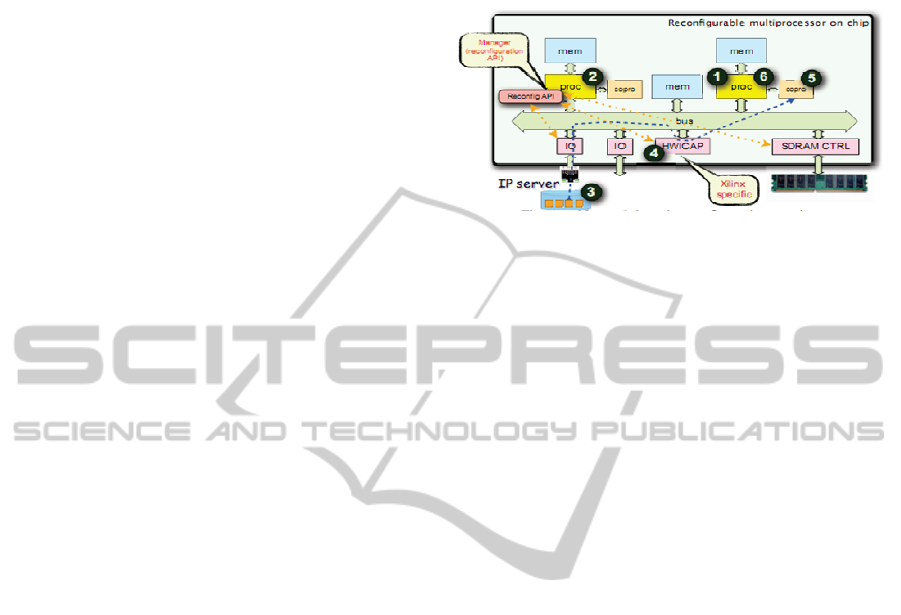

3.3.2 GRACE Project

The GRACE project (Global Resource Adaptation

through CoopEration) (Yuan et al., 2006) (Vardhan

MODELSWARD2013-InternationalConferenceonModel-DrivenEngineeringandSoftwareDevelopment

344

Figure 1: Closed loop adaptive system structure (Diguet

et al., 2011).

et al., 2009) proposes a cross-layer adaptation frame-

work that adapts multiple system layers at multiple

time granularities. It addresses the conflict of adapta-

tion scope and frequency through a hierarchical solu-

tion (c.f.Figure 2) which combines different modules

at different adaptation levels:

• An infrequent expensive global adaptation that

optimizes energy for all applications in the sys-

tem. It only occurs occasionally at large system

changes such as application entry or exit

• A frequent inexpensive limited-scope per-

application adaptation that optimizes for a single

application at a time. It is invoked every frame,

adapting all system layers to the application’s

current demands. An internal adaptation adapts

only a single system layer and may be invoked

several times per application frame.

GRACE’s first generation implementation, called

GRACE-1 (Yuan et al., 2006) coordinates the adap-

tation of the CPU speed in the hardware layer, CPU

scheduling in the OS layer, and multimedia quality in

the application layer, in response to system changes at

both fine and coarse time granularities. It focused also

on the coordination between these cross-layer adapta-

tions in order to reap their full benefit. GRACE-1’s

focus was on cross-layer global adaptation, for which

it showedsignificant energy benefits. It reported a few

experiments with hierarchical adaptation in the CPU

and scheduler, but showed only modest benefits over

global adaptation when running multiple applications.

Later, a second generation prototype, GRACE-2

(Vardhan et al., 2009) was developed to demonstrate

the benefits of the hierarchical adaptation. This pro-

totype implements a global adaptation in the CPU

and application layers, and soft real-time scheduler,

per-app adaptation in both CPU and application lay-

ers, and internal adaptation in the scheduler. It re-

spects the constraints of CPU utilization and network

bandwidth (assumed to be constant), while minimiz-

ing CPU and network transmission energy. GRACE-2

is network-aware. It adds a network bandwidth con-

straint in the global and per-application controller and

considers global and per-application adaptations that

are driven by the tradeoff in CPU time and network

bandwidth usage. It has demonstrated that the lack of

any network awareness results in very modest benefits

from the hierarchical adaptation while running multi-

ple applications. It has also shown that in a network

bandwidth constrained environment, per-app applica-

tion adaptation yields significant energy benefits over

and above global adaptation. This project is very in-

teresting since it has covered almost all system layers.

However, it has been essentially applied to servers

which are not embedded systems and daptation cost

has not been taken into account.

Figure 2: GRACE adaptation structure (Vardhan et al.,

2009).

4 MDE BASED ADAPTATION

APPROACHES

Researches on embedded systems modeling using

MDE approach have begun several years ago and

have shown the gain of using UML/MARTE standard

(Schmidt, 2006) (Dekeyser et al., 2005). However,

those particularly tackling adaptive embedded sys-

tems have recently begun. In the present study, we are

interested on adaptation modeling for embedded sys-

tems using UML/MARTE profile. Currently, most of

state-of-the-art works are focused on modeling hard-

ware level adaptation through system reconfiguration,

but few are interested in software level adaptation, or

furthermore, in cross-layer adaptation modeling. In

the sub-sections below, we present an overview of

the MDE methodology and the MARTE profile, and

then we recall works related to MDE based adaptation

modeling that we classify in hardware and software

levels.

HighLevelDesignofAdaptiveReal-timeEmbeddedSystems-ASurvey

345

4.1 Model Driven Engineering

Overview

Several co-design methodologies shown in literature

prove MDE to be well appropriate to embedded sys-

tems design. The model development process aims at

decreasing the growing complexity of real time sys-

tems as well as the verification of their correctness.

In fact, the abstraction view presented by the model

avoids dealing with details and favorites reusability.

An MDE based methodology starts with a high ab-

straction level and leads to a targeted specific model

through a set of transformations and refinements. The

produced models can be executed to ensure simula-

tion, verification or execution. They can be used for

another objective by being an input to produce other

models.

One variant of MDE is the extension or the restric-

tion of UML views for specific domains. It is pre-

sented through the notion of UML profile. From cur-

rent times, the Object Management Group (OMG) has

voted for a new standard for model driven develop-

ment and analysis of real time systems. The adopted

MARTE (Group, 2011) profile provides mechanisms

to model appropriate specification in order to per-

form specific analysis. In fact, MARTE consists of

three major packages. Foundation Package repre-

sents the foundational concepts for RTES design. It

allows the specification of basic real time concepts

such as non-functional properties (NFPs), time con-

straints and useful resources. The other two pack-

ages are refined from the first one. The second pack-

age named MARTE Design Model is dedicated for

a detailed hardware and software description. As

for the third package, MARTE Analysis Model pack-

age, it offers annotations for generic basis of quanti-

tative performance and schedulability analysis. How-

ever, although it covers a large set of RTES features,

MARTE still lacks concepts for an entire specification

of adaptive RTES, specifically adaptive real-time task

specification and tasks migration for multiprocessor

architectures.

4.2 Hardware Level Adaptation

Modeling

Reconfigurable systems’ modeling is treated by sev-

eral researchers and teams (Rafiq Quadri et al., 2009),

(Rafiq Quadri et al., 2010), (Quadri et al., 2010), (Vi-

dal et al., 2010), (Vidal et al., 2011). A recent project

called FAMOUS (Famous Project, ) is interested in

this topic and involves many partners from research

and industry. It aims at defining a complete design

flow for embedded systems which integrates the dy-

namic reconfiguration of the hardware. We recall in

the subsections below a number of approaches that

have been developed under renowned projects and es-

sentially dealt with dynamic and partial reconfigura-

tion in embedded systems.

4.2.1 Reconfigurability under GASPARD

Framework

Imran et al. proposed in (Rafiq Quadri et al., 2009),

(Rafiq Quadri et al., 2010) a SoC co-design ap-

proach, developed in the GASPARD (Gamatié et al.,

2008) framework, where they integrate control mod-

els based on mode automata to express DPR in mod-

ern FPGA. Xilinx FPGA is the targeted technology.

They present some basic control semantics, such as

Mode Switch Component and State Graphs that are

used in a compositional manner to form mode au-

tomata. Then they propose A UML/MARTE design

flow for automatic RTL code generation to imple-

ment dynamically reconfigurable FPGA. They have

extended the MARTE profile by a set of stereotypes to

model DPR features in Xilinx FPGA. To have a more

complete set of concepts for high level FPGA mod-

eling, they brought, for example, modification to the

HwProcessor stereotype by adding the attribute Im-

plementation_Type to specify wether the processor is

implemented as a hardcore or a softcore IP. Then, to

integrate DPR features, they made modifications to

the HwComponent stereotype such as adding the at-

tribute areatype to specify wether the hardware com-

ponent is a static or dynamically reconfigurable re-

gion or other. They have also defined other exten-

sions to support some Xilinx specific concepts such

as bus macro, which permits routing between static

and reconfigurable regions, the Internal Reconfigura-

tion Access Port (ICAP), which assures the configu-

ration memory read/write at run-time and the Recon-

figurable Hardware Accelerator (RHA). Some con-

trol mechanisms have been added in (Cherif et al.,

2011). A distributed modular reconfiguration con-

troller has been presented. A reconfiguration con-

troller can be defined in differentforms such as a HDL

hardware component or a soft-core processor. It can

also be integrated in different system layers. Here,

the controller has been integrated at the architecture

layer. The complete modeling of a DPR-supported

architecture has been elaborated using the extended

UML/MARTE profile and targeting the Xilinx FPGA

XC2VP30 Virtex-II Pro chip. Model transformations

are applied to move to lower RTL detailed models ar-

riving to automatic code generation of target applica-

tion and the reconfiguration controller.

Although it provides rich extensions of the

MARTE profile to get a more complete support for

MODELSWARD2013-InternationalConferenceonModel-DrivenEngineeringandSoftwareDevelopment

346

dynamically reconfigurable systems, this methodol-

ogy presents some limitations. First, the proposed

system models only focused on the hardware prop-

erties; the MARTE package that has been most exam-

ined and modified is the Hardware Resource Model

(HRM) package. Second, the approach is linked to

the Gaspard framework, and thus limited to a specific

application domain, that of complex intensive data-

parallel applications. Finally, the work is platform-

dependent. It is based on the Xilinx EAPR (Early Ac-

cess Partial Reconfigurable) design methodology and

proposes DPR models at a low level using Xilinx spe-

cific modules. This demands a high level of expertise

and limits its large adoption in future reconfigurable

architectures.

4.2.2 DPR for MPSoPC under MoPCOM

Project

Another co-design methodology targeting the design

and code generation of dynamically reconfigurable

embedded systems has been developed under the

MoPCOM project (Koudri et al., 2008). Authors

tried to be less target-dependent by hiding technol-

ogy specific details at high level models and allow-

ing their adding at code generation level via a target-

dependent code generation tool. In (Vidal et al., 2010)

authors aim at modeling DPR in case of Multiproces-

sor System on Programmable Chip (MPSoPC). Their

approach is based on run-time reconfiguration of co-

processors connected to embedded processors. They

define the three common Y-chart models, the applica-

tion, architecture and allocation models using stan-

dard UML/MARTE stereotypes. The dynamic re-

configuration behavior is integrated in the allocation

model. Specific stereotypes are used to give recon-

figuration indications for the code generation tool. A

«Reconfig» stereotype with an ID tag are added to ap-

plication components to order the integration of a re-

configuration service in the allocated processor code.

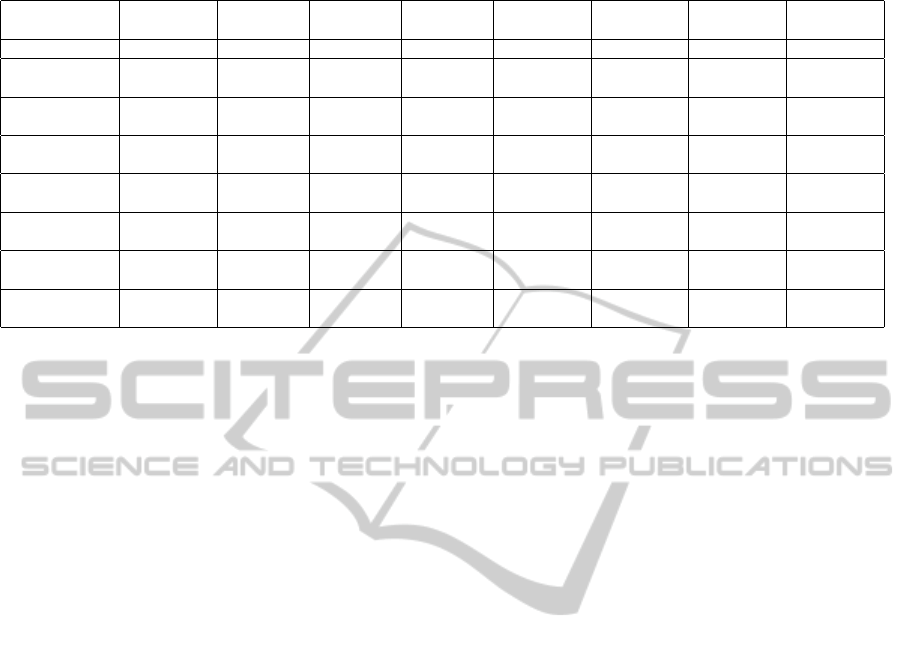

In (Vidal et al., 2011), a component-based mod-

eling methodology is presented. UML/MARTE ele-

ments and some predefined design patterns (Strategy

and state patterns) have been used to reconfigurable

systems. A network based reconfiguration service has

been developed. The proposed reconfigurable MP-

SoPC is illustrated in Figure 3. One of the processors

is identified as a «manager processor» which executes

the reconfiguration API. When a processor wants to

reconfigure its co-processor,it sends a reconfiguration

request to the manager processor. This latter loads the

requested bitstream either from a SDRAM cache or,

if it doesn’t exist locally, from an IP server connected

to the chip through an Ethernet connection. Using

the PlanAhead design and analysis tool, a bitstream

is generated for the initial system configuration and

a set of partial bitstreams are made for each possible

configuration.

Figure 3: Reconfiguration service integration in MPSoPC

(Vidal et al., 2011).

Furthermore, while authors claim to consider real-

time components by using the «RTUnit» stereotype,

they express no special care for the real-time con-

straint. Their allocated model is manually performed,

so it gives no guarantee about the optimality of the

selected solution. A design space exploration step

and a schedulability analysis are thus necessary to

be added in order to fit to modern complex systems

which present dynamic tasks sets with timing con-

straints.

The presented approaches set important basis for

dynamic reconfiguration support in embedded sys-

tems using high level design methodology. How-

ever, in order to efficiently uphold this capability,

some control and decision making mechanisms need

to be considered. These approaches are only inter-

ested in DPR modeling without tackling the adapta-

tion engine which lies behind the reconfiguration de-

cisions such as events, adaptation rules, system moni-

tors, adaptation managers and assessor. Additionally,

the reconfiguration capability is only developed for

the hardware platform. The application behavior is

unchanged and tasks scheduling is static. Further-

more, these works exhibit no support for real-time

constraints and performance evaluation.

4.3 Software-level Adaptation Modeling

We present hereafter two recent works among the

few ones tackling MDE based adaptation modeling

at software level.

A model based approach is provided in (Krichen

et al., 2010) to deal with software reconfiguration in

distributed real-time embedded (DRE) systems with

respect to non-functional properties. Authors started

from the fact that MARTE and AADL standards

present the limitation of permitting dynamic recon-

figuration modeling for RTES by using only static

sets of predefined modes (also called configurations)

HighLevelDesignofAdaptiveReal-timeEmbeddedSystems-ASurvey

347

Table 1: Comparison of adaptation approaches for RTES.

UML/MARTE Platform in-

dependent

Multiprocessor Modularity Hw/Sw Adap-

tation

Design-time

verif.

Online time

verif.

Online perfor-

mance eval.

(Ye et al., 2010) * *

(Diguet et al.,

2011)

* * * * *

(Vardhan et al.,

2009)

* * * *

(Rafiq Quadri

et al., 2010)

* *

(Cherif et al.,

2011)

* * *

(Vidal et al.,

2011)

* *

(Krichen et al.,

2010)

* * * *

(Boukhanoufa

et al., 2011)

* * *

and transitions between them. Thus, they proposed

a reconfiguration approach with non-predefined set

of possible configurations by capturing them using

mode structure concept. To describe this concept,

they defined a simple MARTE and AADL inspired

meta-model for reconfigurable software architectures

in RTES which is a combination of model and com-

ponent paradigms. The reconfigurable DRE system

is modeled by a set of mode structures. A transition

between mode structures specifies a reconfiguration

activity which is activated by an event trigger and re-

lated to some constraints. The proposed meta-model

is composed of three packages permitting to define

three adaptation features: the configurationstructures,

the possible events and the reconfiguration activities.

A UML profile for reconfigurable DRE was derived

from this meta-model. This work was enhanced in

(Krichen et al., 2011) by adding a fourth package to

specify Structural and non-functional constraints and

allocation constraints (policies of meta-modes alloca-

tion on execution supports). Another improvement

was added in (Krichen et al., 2012) which consists in

a verification approach for reconfigurable DRE sys-

tems permitting to verify, at design time, a set of

non-functional properties such as CPU usage, mem-

ory and bandwidth usage,tasks deadline meeting, and

deadlock and livelock freedom. They used the RMS

scheduling algorithm, the Cheddar framework and

defined algorithms for verification of the mentioned

properties. This approach adds precious features to

adaptation support using MARTE profile but is only

limited to software modeling. The hardware architec-

ture is considered unchanged. It also lacks support for

online temporal verification and performance evalua-

tion of adaptation.

(Boukhanoufa et al., 2010) (Boukhanoufa et al.,

2011) were also interested in software adaptation

modeling using UML/MARTE. They essentially fo-

cused on the validation of adaptation rules with re-

spect to real-time constraints at design time. A state

machine is used to model the application configura-

tions and transitions between them. Time constraints

verification is performed via a simple comparison be-

tween the worst case execution time of adaptation op-

erations with the application allocated time slot. This

work is among rare researches that have dealt with

timing constraints at model analysis step. However, it

is an off-line step where time constraints verification

is performed on the basis of a set of unchanged timing

properties, which does not fit dynamic systems with

variable input data and resource constraints (variable

execution times and WCET).

5 DISCUSSION

In this section, we present a comparative Table 1

which summarizes related works on adaptive embed-

ded systems and compares them according to the cri-

teria described in section 2. We derive from the pre-

vious study that most of MDE-based adaptation ap-

proaches tackle only hardware level adaptation mod-

eling, essentially dynamic hardware reconfiguration

(Reconfigurable architectures, modes and transitions

modeling), whereas few interests exist in modeling

adaptation at the software level. Cross layer adap-

tation is absent in MDE approaches. Along with this

deficiency, MARTE does not support, among others,

adaptive real-time tasks specification and interproces-

sor tasks migration. We therefore need to add ex-

tensions to MARTE to permit a generic and com-

plete adaptivity features modeling in different system

layers. We need to proceed towards efficient imple-

mentations of adaptive embedded systems through a

well defined design flow which uses a common lan-

guage to avoid misunderstandings between designers,

MODELSWARD2013-InternationalConferenceonModel-DrivenEngineeringandSoftwareDevelopment

348

and permits the elevation of abstraction level, separa-

tion of functional and extra-functional concerns, and

reusability.

Furthermore, most of existing approaches do not

support the complete process of adaptation for real

time embedded systems and lack modularity. They

present a few interest in temporal properties con-

trol, which present a major constraint in RTES, as

well as performance evaluation. More efforts need

then to be done in the assessment step through tem-

poral and performance analysis models in order to

build more efficient and reliable systems.To the best

of our knowledge, none of existing MDE approaches

jointly dealt with the following features: adaptive

RTES HW/SW modeling, MDE, UML/MARTE pro-

file, modular adaptation process, online temporal ver-

ification and performance analysis. The gathering of

these features in a complete design flow, from high

abstraction level modeling to implementation, sets the

originality of our future works.

6 CONCLUSIONS

According to our study around adaptive embedded

systems, we notice a gap between adaptation tech-

niques development and their utilization in embed-

ded systems. This gap is due to compatibility and

reusability issues and the complexity of integration of

adaptive behavior in increasingly complex systems.

Unfortunately, the limitation of computer aided de-

sign tools addressing adaptive embedded systems de-

sign further widens the gap. To deal with these issues,

specialists in the field have resorted to MDE based

design methodologies. The UML/MARTE profile is

the most upcoming standard for model-driven devel-

opment of embedded systems. It permits to model

the properties of software and hardware parts of a

RTES and the relations between them. It also offers

some extensions such as performance and scheduling

analysis. However, although it offers a large set of

RTES features, MARTE still lacks a full specification

of adaptive RTES.

Our work-in-progress does not consist in propos-

ing a new adaptation approach, but lies in drawing

up a complete design flow that raises the adaptation

RTES development to a high abstraction level, based

on MDE and UML/MARTE standards. Our aim is

to set a generic modeling tool for adaptive RTES

through MARTE extension which (a) permits mod-

els reusability and design complexity decrease and

(b) covers the adaptation process modules, with spe-

cial focus on online temporal verification and perfor-

mance assessment. This approach can then be utilized

by designers who contribute to the embedded systems

adaptation field.

REFERENCES

Banachowski, S. A. and Brandt, S. A. (2002). The best

scheduler for integrated processing of best-effort and

soft real-time processes. In In Proceedings of Multi-

media Computing and Networking 2002 (MMCN Š02,

pages 46–60.

Boukhanoufa, M.-L., Radermacher, A., and Terrier, F.

(2010). Towards a model-driven engineering approach

for developing adaptive real-time embedded systems.

In NOTERE, pages 261–266.

Boukhanoufa, M.-L., Radermacher, A., and Terrier, F.

(2011). Offline validation of real-time application

constraints considering adaptation rules. In Proceed-

ings of the 2011IEEE 10th International Conference

on Trust, Security and Privacy in Computing and

Communications, TRUSTCOM 11, pages 974–980,

Washington, DC, USA. IEEE Computer Society.

Cherif, S., Trabelsi, C., Meftali, S., and Dekeyser, J.-L.

(2011). High level design of adaptive distributed con-

troller for partial dynamic reconfiguration in fpga. In

DASIP, pages 308–315.

Chu, H.-H. and Nahrstedt, K. (1999). Cpu service classes

for multimedia applications. In ICMCS, Vol. 1, pages

296–301.

Dekeyser, J.-L., Boulet, P., Marquet, P., and Meftali, S.

(2005). Model Driven Engineering for SoC Co-

Design. In NEWCAS’05, Quebec, Canada. IEEE.

Diguet, J.-P., Eustache, Y., and Gogniat, G. (2011).

Closed-loop–based self-adaptive hardware/software-

embedded systems: Design methodology and smart

cam case study. ACM Trans. Embed. Comput. Syst.,

10(3):38:1–38:28.

Famous Project. Anr famous overview.

Gamatié, A., Le Beux, S., Piel, É., Etien, A., Ben Atitallah,

R., Marquet, P., and Dekeyser, J.-L. (2008). A Model

Driven Design Framework for High Performance Em-

bedded Systems. Research Report RR-6614, INRIA.

Gogniat, G., Vidal, J., Ye, L., Crenne, J., Guillet, S.,

de Lamotte, F., Diguet, J.-P., and Bomel, P. (2010).

Self-reconfigurable embedded systems: From model-

ing to implementation. In ERSA, pages 84–96.

Goossens, J., Funk, S., and Baruah, S. (2003). Priority-

driven scheduling of periodic task systems on multi-

processors. Real-Time Syst., 25:187–205.

Group, O. O. M. (June 2011). A UML Profile for MARTE:

Modeling and Analysis of Real-Time Embedded sys-

tems, ptc/2011-06-02. Object Management Group.

Hsia, S.-C. (2003). An adaptive video coding control

scheme for real-time mpeg applications. EURASIP J.

Appl. Signal Process., 2003:244–251.

Koudri, A., Vojtsiek, D., Soulard, P., Moy, C., Champeau,

J., Vidal, J., and Le Lann, J.-c. (2008). Using marte

in the mopcom soc/sopc methodology. In workshop

MARTE.

HighLevelDesignofAdaptiveReal-timeEmbeddedSystems-ASurvey

349

Krichen, F., Hamid, B., Zalila, B., and Coulette, B.

(2010). Designing dynamic reconfiguration for dis-

tributed real time embedded systems. In NOTERE,

pages 249–254.

Krichen, F., Hamid, B., Zalila, B., and Jmaiel, M. (2011).

Towards a model-based approach for reconfigurable

dre systems. In ECSA, pages 295–302.

Krichen, F., Hamid, B., Zalila, B., and Jmaiel, M. (2012).

Design-time verification of reconfigurable real-time

embedded systems. In HPCC-ICESS, pages 1487–

1494.

Loukil, K., Amor, N. B., Said, M. B., and Abid, M. (2009).

Os service update for an online adaptive embedded

multimedia system. In ISCC, pages 721–725.

Mesarina, M. and Turner, Y. (2003). Reduced energy decod-

ing of mpeg streams. Multimedia Syst., 9(2):202–213.

Mohapatra, S. and Venkatasubramanian, N. (2003). Parm:

Power aware reconfigurable middleware. In Proceed-

ings of the 23rd International Conference on Dis-

tributed Computing Systems, ICDCS ’03, pages 312–,

Washington, DC, USA. IEEE Computer Society.

Ngoc, N. P., van Raemdonck, W., Lafruit, G., Deconinck,

G., and Lauwereins, R. (2002). A qos framework for

interactive 3d applications. In WSCG, pages 317–324.

Pillai, P., Huang, H., and Shin, K. G. (2003). Energy-aware

quality of service adaptation. Technical report, UNIV.

OF MICHIGAN.

Pillai, P. and Shin, K. G. (2001). Real-time dynamic voltage

scaling for low-power embedded operating systems.

SIGOPS Oper. Syst. Rev., 35(5):89–102.

Quadri, I. R., Meftali, S., and Dekeyser, J.-L. (2010). De-

signing dynamically reconfigurable socs: From uml

marte models to automatic code generation. In DASIP,

pages 68–75.

Rafiq Quadri, I., Meftali, S., and Dekeyser, J.-L. (2009).

A Model based design flow for Dynamic Reconfig-

urable FPGAs. International Journal of Reconfig-

urable Computing.

Rafiq Quadri, I., Yu, H., Gamatié, A., Rutten, E., Meftali,

S., and Dekeyser, J.-L. (2010). Targeting Reconfig-

urable FPGA based SoCs using the MARTE UML

profile: from high abstraction levels to code genera-

tion. Special Issue on Reconfigurable and Multicore

Embedded Systems, International Journal of Embed-

ded Systems (IJES).

Said, M. B., Amor, N. B., Taher, F. B., Diguet, J. P., and

Abid, M. (7-9 April 2011). A bi-constraints adapta-

tion technique for embedded multimedia systems. In

International Conference on Multimedia Computing

and Systems (ICMCS), 2011, pages 1 – 6.

Satyanarayanan, M., Noble, B., Kumar, P., and Price, M.

(1995). Application-aware adaptation for mobile com-

puting. SIGOPS Oper. Syst. Rev., 29(1):52–55.

Schmidt, D. C. (2006). Model-driven engineering. IEEE

Computer, 39(2).

Vahdat, A., Lebeck, A., and Ellis, C. S. (2000). Every joule

is precious: the case for revisiting operating system

design for energy efficiency. In EW 9: Proceedings of

the 9th workshop on ACM SIGOPS European work-

shop, pages 31–36, New York, NY, USA. ACM Press.

Vardhan, V., Yuan, W., III, A. F. H., Adve, S. V., Kravets, R.,

Nahrstedt, K., Sachs, D. G., and Jones, D. L. (2009).

Grace-2: integrating fine-grained application adapta-

tion with global adaptation for saving energy. IJES,

pages 152–169.

Vidal, J., de Lamotte, F., Gogniat, G., Diguet, J.-P., and

Guillet, S. (2011). Dynamic applications on recon-

figurable systems: From uml model design to fpgas

implementation. In DATE, pages 1208–1211.

Vidal, J., de Lamotte, F., Gogniat, G., Diguet, J.-P., and

Soulard, P. (2010). Uml design for dynamically re-

configurable multiprocessor embedded systems. In

Proceedings of the Conference on Design, Automation

and Test in Europe, DATE 10, pages 1195–1200, 3001

Leuven, Belgium, Belgium. European Design and Au-

tomation Association.

Ye, L., Diguet, J.-P., and Gogniat, G. (2010). Rapid appli-

cation development on multi-processor reconfigurable

systems. In FPL, pages 285–290.

Yuan, W. and Nahrstedt, K. (2006). Energy-efficient cpu

scheduling for multimedia applications. ACM Trans.

Comput. Syst., 24(3):292–331.

Yuan, W., Nahrstedt, K., Adve, S. V., Jones, D. L., and

Kravets, R. H. (2006). Grace-1: Cross-layer adapta-

tion for multimedia quality and battery energy. IEEE

Transactions on Mobile Computing, 5(7):799–815.

MODELSWARD2013-InternationalConferenceonModel-DrivenEngineeringandSoftwareDevelopment

350