ECG Pattern Recognition and Beat Classification using Internet of

Things and Hardware Acceleration on ZynQ (SOC) Platform with

High Performance Computational PCIe Protocol

Vijendra V.

1

, Meghana Kulkarni

1

and Rajesh Murgan

2

1

Center for PG Studies, Dept. of VLSI Design & Embedded Systems, Visvesvaraya Technological University,

Belgaum, Karnataka, India

2

CoreEL Technologies (I) Pvt Ltd , Bangalore, India

Keywords: ZynQ System on Chip (SoC), Internet of Things (IoT), Think Speak Cloud, Object Identification, Dynamic

Reconfigure Port (DRP), Transmission Control Protocol/Internet Protocol, Peripheral Component

Interconnect Express (PCIe), Direct Memory Access.

Abstract: The ECG signals plays an important vital role in Diagnostics Systems. The Real time Hardware

Implementation Provides Accuracy, speed, Beat classification, predictivity and diagnostics of the system

Interpretation and classification The ECG Signal extraction from sensor and Processing on the Zynq SoC

Platform and Imported on to the cloud in involves three Steps: i) Real time data fetch from the Sensor device

ii) Pushing on to the Cloud uproot Using TCP/IP Protocol iii) Cloud IDE Processing Using SDAccel openCL

language with Amazon FPGA Image (AFI) on Virtual servers with the help of openCL/C++ libraries, Xilinx

SDx Environments and virtual JTAG interfaces on Xilinx Virtex Ultrascale Plus Board(VU9P) low profile

PCIe accelerated Board.

1 INTRODUCTION

ECG signal are important for detection of crucial

heart diseases and Continues monitoring system will

help in identification of prolonged chest pain and

other related diseases like heart attack stages and their

Symptoms. There are different diagnostics systems

like holter monitor, traditional diagnostics systems.

ECG beat annotation signals provides the

information on chemical imbalance, prolonged

medication and drug addictions. There are different

algorithm like Partial swam Optimization (PSO),

Fuzzy models, ANFIS provides that better analysis

and realistic outputs.

2 METHODOLOGY

1. IoT Based ECG Analog input signal from XADC

port or using sensors Temperature transmission

using ZynQ Board

2. Loading the ECG Signals from SDcard

(Standalone) from ThingSpeak Cloud

3. Transmitting Through the UDP Port

4. Processing the ECG Signals from Python Yolo

frame work and Filtering the ECG Signals.

5. DMA using PCIe Implementation Using Xilinx

Vivado IP based design and SDK Environment.

6. Cloud IDE Processing Using SDAccel openCL

language with Amazon FPGA Image (AFI).

7. Virtual servers with the help of openCL/C++

libraries, Xilinx SDx Environments and virtual

JTAG interfaces on Xilinx Virtex Ultrascale Plus

Board(VU9P) low profile PCIe accelerated

Board.

V., V., Kulkarni, M. and Murgan, R.

ECG Pattern Recognition and Beat Classification using Internet of Things and Hardware Acceleration on ZynQ (SOC) Platform with High Performance Computational PCIe Protocol.

DOI: 10.5220/0007576902610268

In Proceedings of the 12th International Joint Conference on Biomedical Engineering Systems and Technologies (BIOSTEC 2019), pages 261-268

ISBN: 978-989-758-353-7

Copyright

c

2019 by SCITEPRESS – Science and Technology Publications, Lda. All rights reserved

261

2.1 Operations

i) XADC performs Analog to Digital Conversion, ii)

Measure the Onchip Temperatures and Voltages , iii)

Set alarms for performance.

2.2 Interface Supports

• AXI4 lite

• Dynamic Reconfigurable Port (DRP)

• AXI Stream

Loading the ECG signals in Analog Sim options in

DRP Timing panel, You can able to load the CSV or

text file consists of Integer values.

The Re-customization of XADC Wizard Consists

of two ADC Converts in that one for Temperature

sensor and another for External Analog ECG signals

and Multiplexed with 12-bit 1MSPS resolution of

data conversion and loading on to the Registers banks

The Sensors will detect the On chip temperatures,

Voltages of the Chip, Dual 12 bit 1MSPS XADC port

(Analog to Digital Converter) as Vp_0, Vn_0,

Vauxp[0], Vauxn[0] and Voltage Sensor pins. XADC

in Zynq 7000 series will have different sensors to

Check Voltages and Temperature of the chip die.

Zynq SoC will have different banks, in that XADC

pins are located in Bank 0. Dynamic Reconfigure Port

via interface to JTAG to download the bit file. The

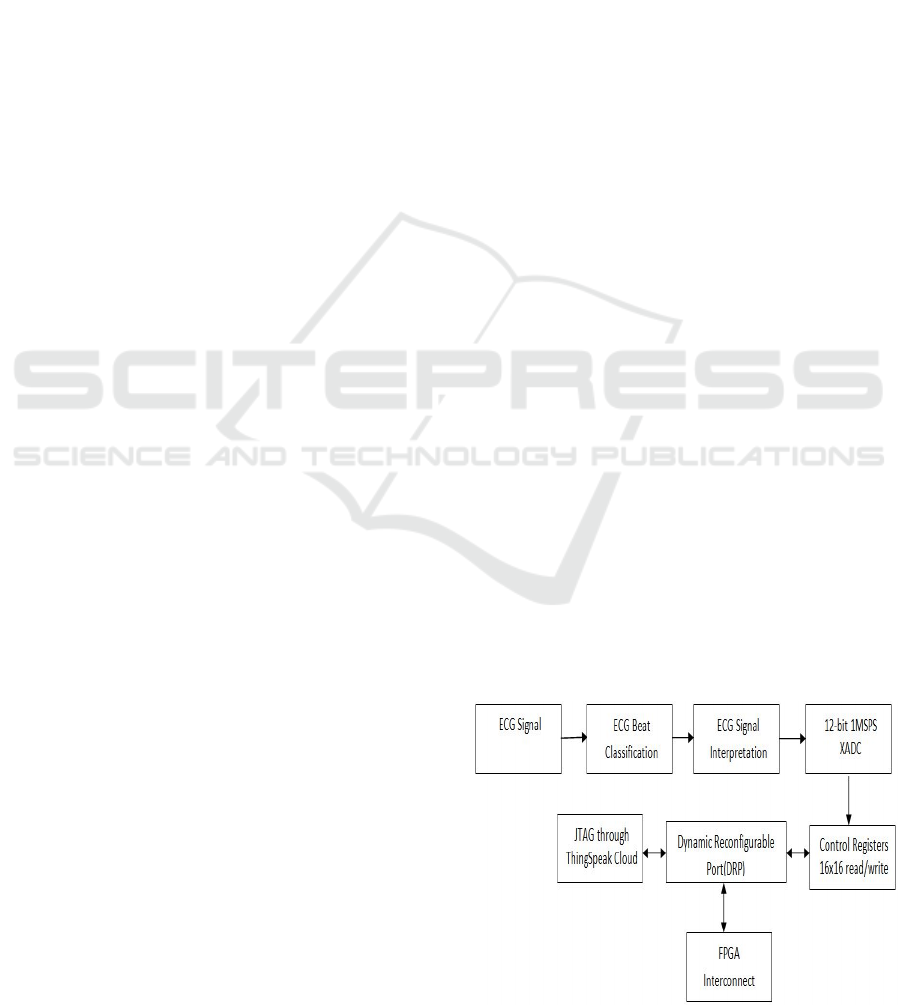

Block of XADC port as shown below in figure 1.

Figure 1: Block diagram of XADC wizard.

The Entire Implementation of ECG Beat

Annotation signals and their Classification Using

Yolo framework using Bayesian classifier.

The ECG signals conversion using Xilinx Vivado

tool with Zynq SOC Platform for Implementation. I)

Zynq Processor acts like master and rest acts like

Peripherals AXI4 Lite, XADC wizard, On top of it

Application code to check the ECG Beat annotation

signals.

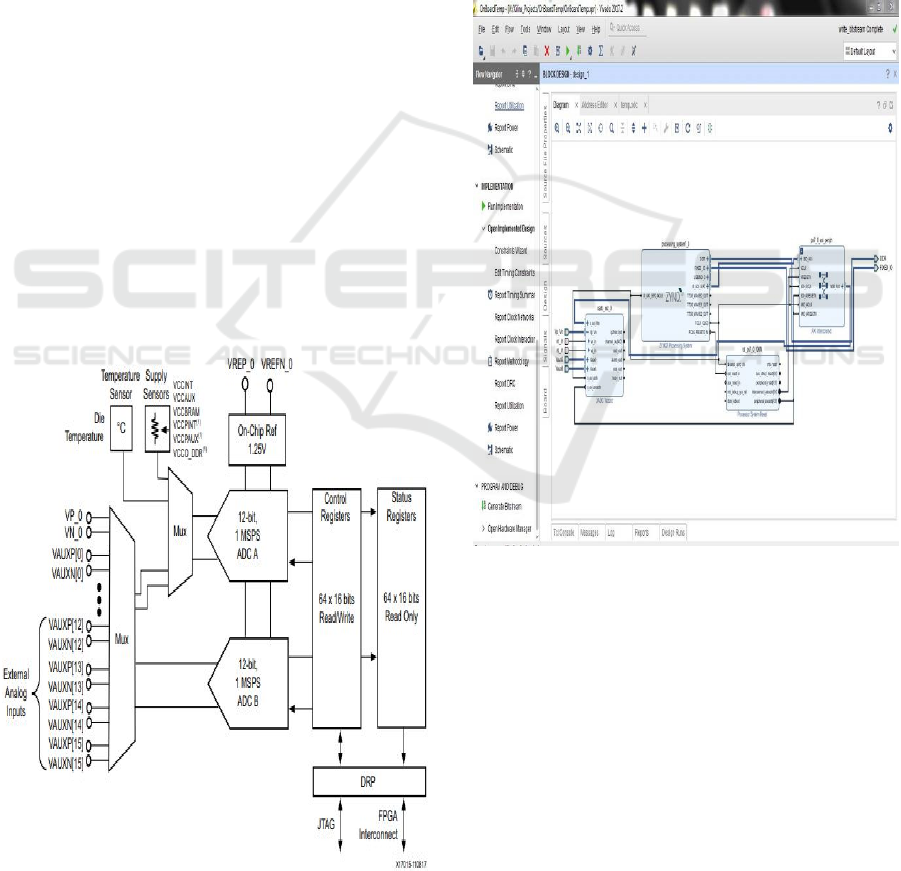

Xilinx Vivado software is used for

Implementation with IP block design, Conversion of

IP design into RTL code using HDL wrappers, shown

below figure 2.

Figure 2: Block design Implementation.

Zynq SOC 7000 series ZedBoard act like a

prototyping devices. Where Synthesis, Implement the

design and Generate the bit file to download on to the

Board.

The IP Based design acts like a building block on

the top OS we need to write an application code C-

code to build the SOC system,

BIODEVICES 2019 - 12th International Conference on Biomedical Electronics and Devices

262

The Program Code as follows-

Application Code:

#include <stdio.h>

#include "platform.h"

#include "xsysmon.h"

#defineSYSMON_DEVICE_ID

XPAR_SYSMON_0_DEVICE_ID

#define XSysMon_RawToExtVoltage(AdcData) \

((((float)(AdcData))*(1.0f))/65536.0f) //(ADC 16bit

result)/16/4096 = (ADC 16bit result)/65536

// voltage value = (ADC 16bit result)/65536 * 1Volt

static XSysMon SysMonInst; //a sysmon instance

static int SysMonFractionToInt(float FloatNum);

int main()

{

u8 SeqMode;

u32

TempRawData,VccIntRawData,ExtVolRawData,i;

float TempData,VccIntData,ExtVolData;

int xStatus;

XSysMon_Config *SysMonConfigPtr;

XSysMon *SysMonInstPtr = &SysMonInst;

init_platform();

print("Hello World\n\r");

SysMonConfigPtr =

XSysMon_LookupConfig(SYSMON_DEVICE_ID)

;

if(SysMonConfigPtr == NULL)

printf("LookupConfig FAILURE\n\r");

xStatus = XSysMon_CfgInitialize(SysMonInstPtr,

SysMonConfigPtr,SysMonConfigPtr->BaseAddress)

;

if(XST_SUCCESS != xStatus) printf("CfgInitialize

FAILED\r\n");

XSysMon_GetStatus(SysMonInstPtr); // Clear the

old status

while(1)

{ //wait until EOS activated

while ((XSysMon_GetStatus(SysMonInstPtr) &

XSM_SR_EOS_MASK) !=

XSM_SR_EOS_MASK);

TempRawData =

XSysMon_GetAdcData(SysMonInstPtr,

XSM_CH_TEMP);//Read the on-chip Temperature

Data

TempData =

XSysMon_RawToTemperature(TempRawData);

printf("\r\nThe Current Temperature is %0d.%03d

Centigrades.\r\n",

(int)(TempData),

SysMonFractionToInt(TempData));

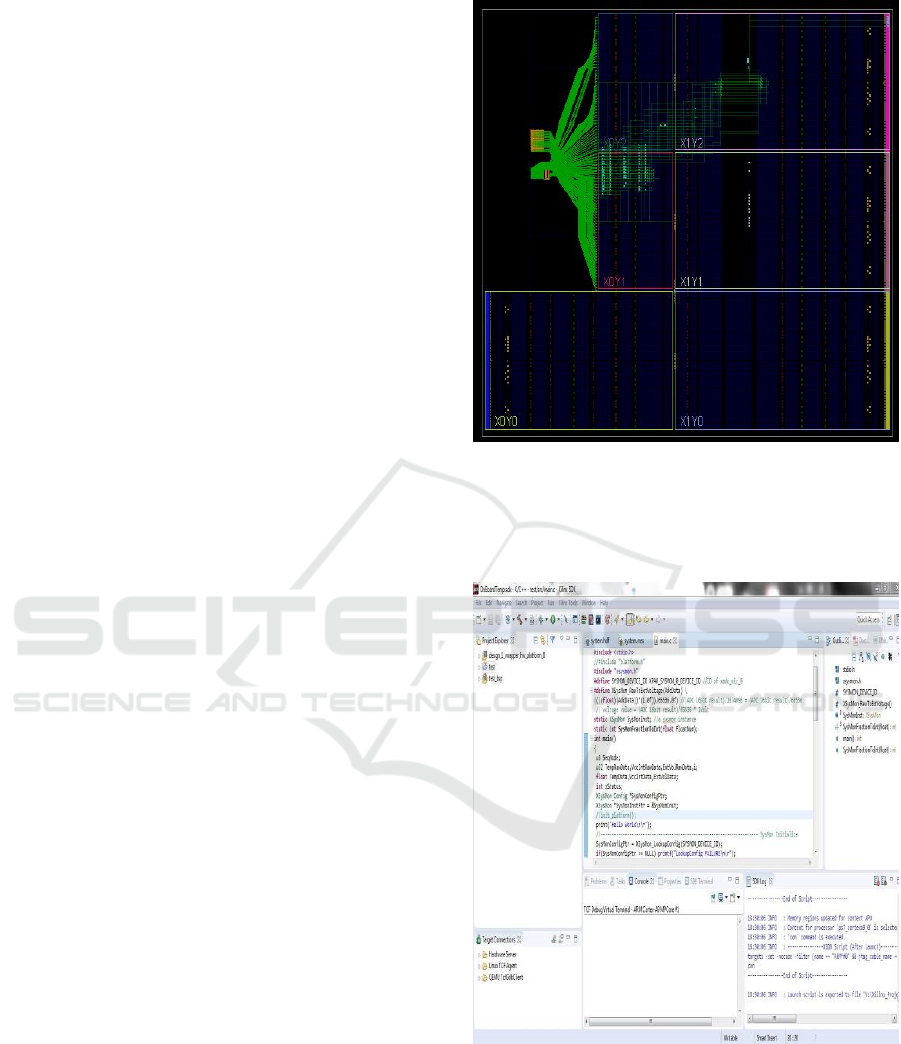

Synthesis output as shown in the figure 3.

Figure 3: Hardware Implementation in PS section.

The Implementation stage the Utilization of area and

Power Consumption reports. XADC banking regions

shown in figure 3.

Figure 4: Application code in SDK platform.

The C-Code Implemented on Xilinx SDK

Platform as shown above and the Communication

using JTAG Port.

ECG Pattern Recognition and Beat Classification using Internet of Things and Hardware Acceleration on ZynQ (SOC) Platform with High

Performance Computational PCIe Protocol

263

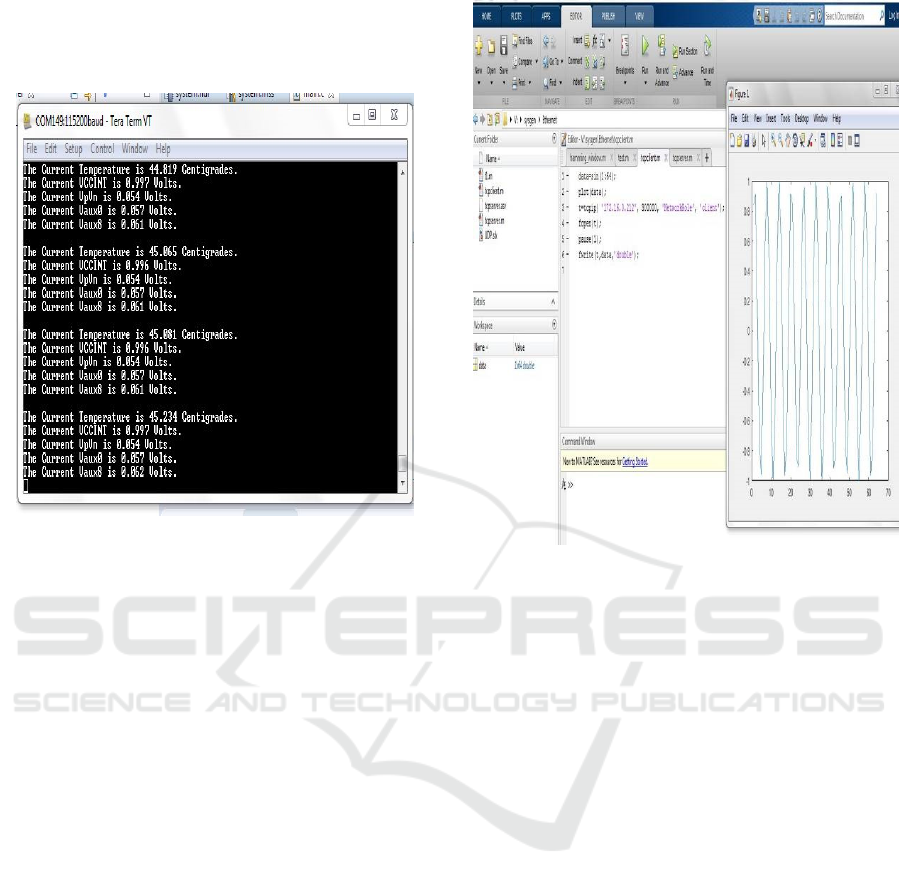

The Serial Terminal using Board rate as 115200,

we can able to communicate the design Analog ECG

signals and Print on the XADC ICAP Port.

Figure 5: UART real time processed data on FPGA.

The ECG Signal from ADC port pushing on to the

serial port of Zynq SOC using Matlab Software and

Convert it as Character.

UDP is a Communication Protocol between the

networks, UDP works on four parameters like Source

port, destination port, length and Check sum.

Implementation of UDP Protocol in simulink design

Using Real time Simulink explorer , UDP send block,

Receive block in the design. UDP doesn't have an

order to track the packets. so TCP/IP protocol is

Implemented in Communication channel to

overcome the packet loss. To Overcome the packet

loss, we use TCP/IP protocol. Transmission Control

Protocol is a communication channel between

Application layer and transport layer. Basically it

work s on the functionality of Byte Streaming,

Connection Oriented, Full duplex, Piggy Backing,

error control, flow control and conjuction control

Mechanism. TCP/IP first priority is to segment the

obtained data from application layer. It works over

Three way hand shaking. Because of which

guarantees the no loss data. Implemented using

MATLAB Script file in two stages as : Transmission

server and client based Remote desktop machines.

Whenever the data is sent to the receiver the flow

should be followed, otherwise receiver will overflow

due to huge data and might be data loss.

Figure 6: TCP/IP client received signal.

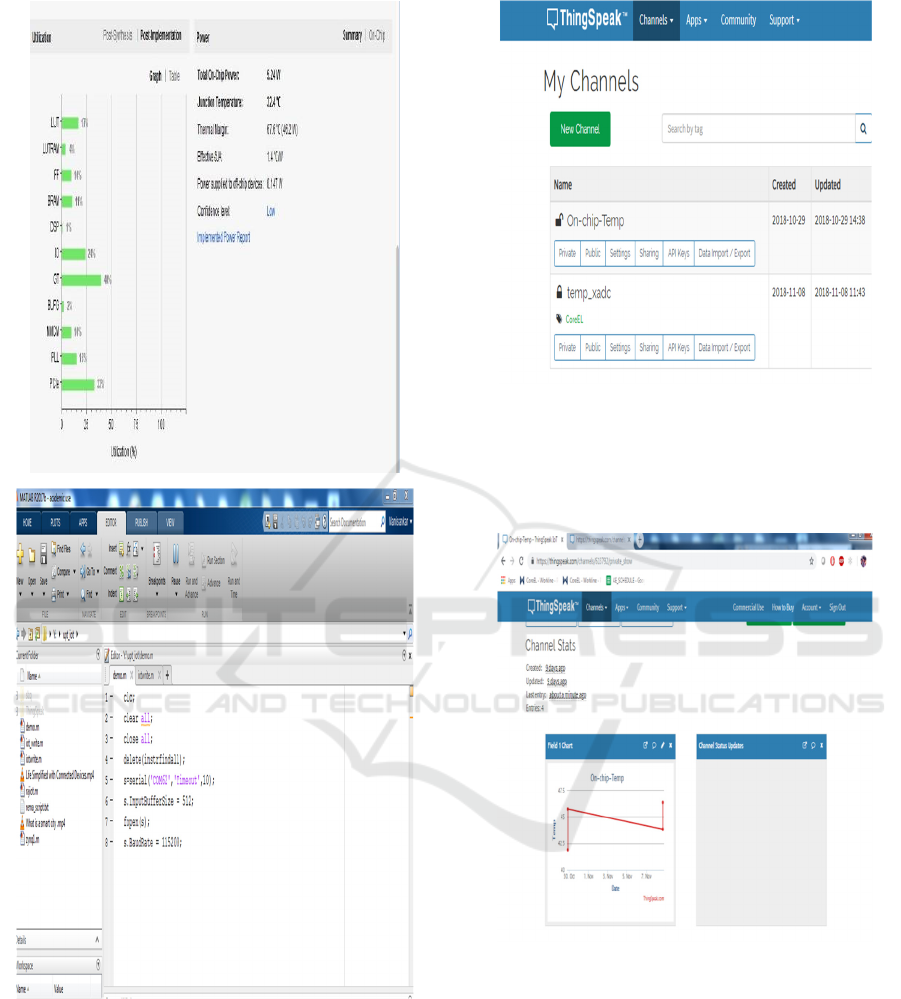

Finally Upload the ECG Annotation signal on to

the Think Speak Cloud to print the live Signals.

XADC wizard in Xilinx Artix7 FPGA has to

convert ADC. It has Voltage and on chip Temperature

Sensor which will monitor the FPGA device. We

Created Zynq Ps and for PL we create XADC IP.

We write an application for the hardware XADC for

On chip temp sensor. We read the temperature value

from UART by PS side. Through Matlab and

ThingSpeak we can read the data from the Xilinx

SDK Application and Update it in the ThingSpeak

Cloud.

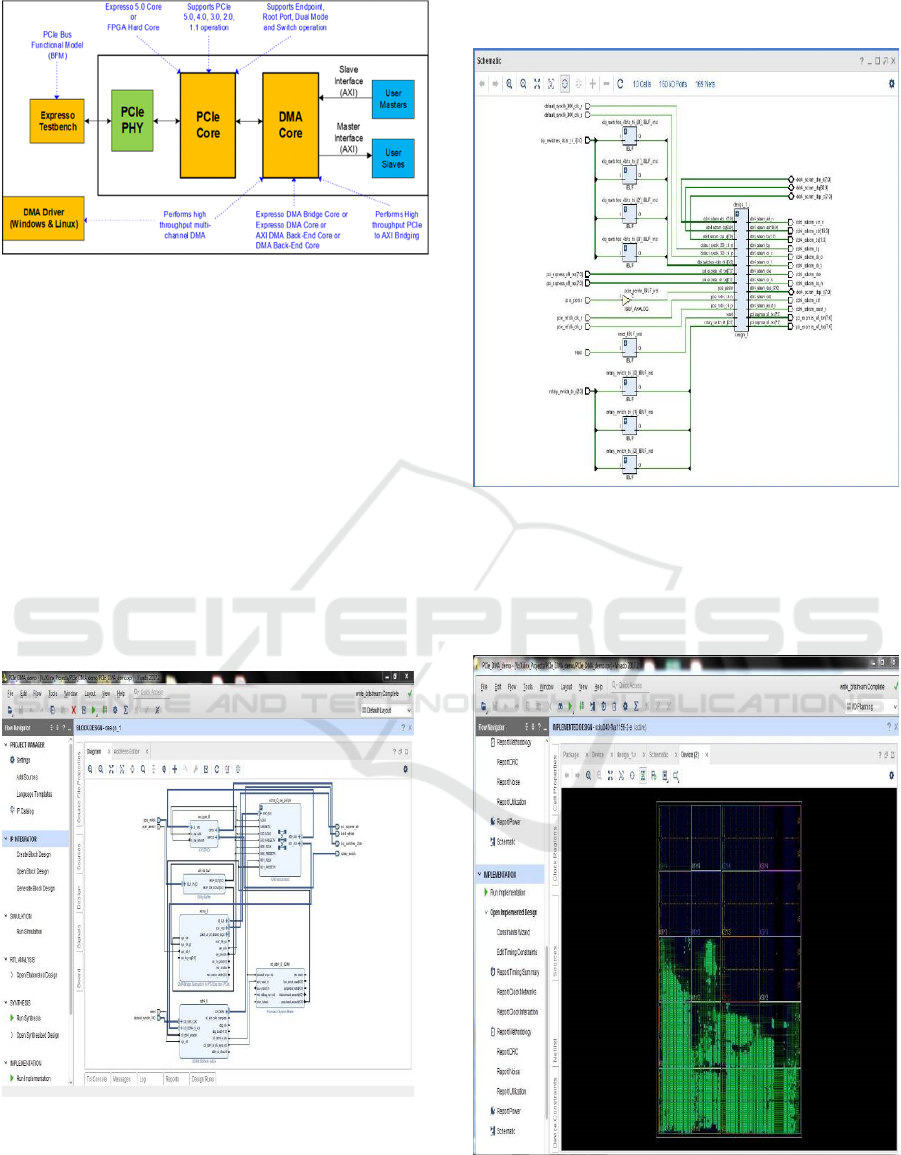

3 DMA FOR PCIE

Direct Memory access for Peripheral Component

Interface Express (PCIe)

BIODEVICES 2019 - 12th International Conference on Biomedical Electronics and Devices

264

Figure 7: Thing Speak Cloud with ECG Uploads as follows.

Advanced eXtensible Interconnect AXI4 -stream,

will provides upto 4 read & 4 write channels.

64/128/256 bit data bus up to 250Mhz Scattered

Block engine.

Implementation of DMA for PCIe using KCU105

board having PCIe slot connect to the host server

systems.

It provides Communication between Host to PCIe

Card & Card to Host machine. The Hardware Blocks

involved are AXI GPIO, DMA/Bridge Subsystem for

PCI Express, AXI Performance Monitor, AXI

BRAM, System ILA, System Management Wizard,

DDR4 SDRAM, Block Memory Generator,

Processing System, and AXI Interconnect block in

Vivado IPI based Model as shown below.

The IPI blocks are Validated with no errors,

Generated input-output products to ger the RTL-

Verilog code for synthesis and Implementation stage

followed by bit file generation and HDF file.

The Schematic Design

Exporting it into Software Development platform

(SDK) Application in C-code to control the API

design.

Design Implementation Stage

Resource Utilization of Hardware system.

ECG Pattern Recognition and Beat Classification using Internet of Things and Hardware Acceleration on ZynQ (SOC) Platform with High

Performance Computational PCIe Protocol

265

Figure 8: ThinkSpeak Cloud Channels.

The Uploaded ECG signals are Processed by Yolo

Frame work Python design using Bayesian Classifier

to identify the ECG Annotation Signals.

Figure 9: Real time data transfer on MATLAB cloud.

BIODEVICES 2019 - 12th International Conference on Biomedical Electronics and Devices

266

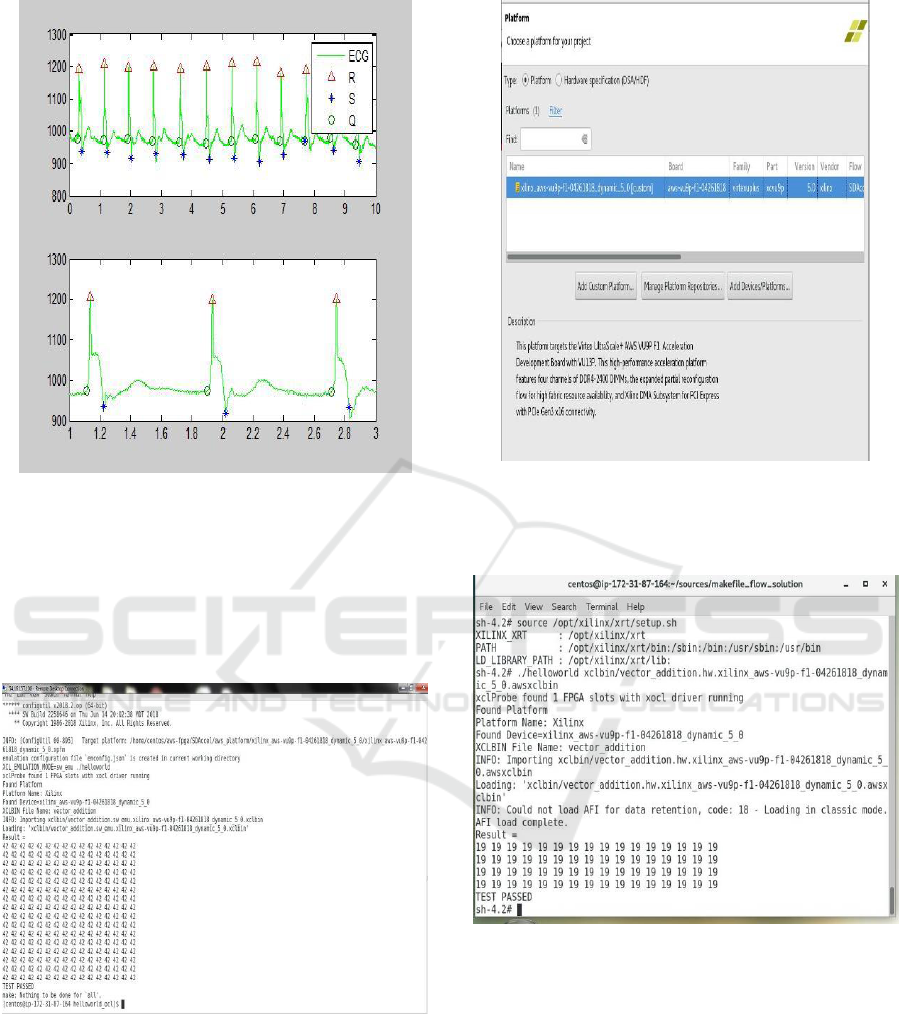

Figure 10: ECG Annotation signals on Cloud.

Cloud Computing Solutions with AWS

Virtual servers with the help of openCL/C++

libraries, Xilinx SDx Environments and virtual JTAG

interfaces on Xilinx Virtex Ultrascale Plus

Board(VU9P) low profile PCIe accelerated Board.

The platform targets the Virtex Ultrascale + AWS

amazon Web services VU9P F1 acceleration

Development with VU13P. The high Performance

acceleration platform features four channels of

DDR4-2400 DIMMs, the expanded partial

reconfiguration flow for high fabric resource

availability and Xilinx DMA subsystem for PCIe

Express with PCIe Gen 3x16 connectivity.

Figure 11: SDx Environment with Hardware XU9P.

AFI Data Retension

Pipelining

The pipeling loop for the PCIe design provides less

number of Execution cycles, real time hardware

acceleration with data speed of PCIe x8 Gen 3 8GT/s,

width x8.

ECG Pattern Recognition and Beat Classification using Internet of Things and Hardware Acceleration on ZynQ (SOC) Platform with High

Performance Computational PCIe Protocol

267

4 CONCLUSION

The IoT Based design will give the Optimized

Solution and Diagnostics capabilities for the benefit

of humans. The PSO Techniques and Fuzzy

Interpretation using Cloud Processing help in saves

thousands of lives. The Hardware platform gives real

time on chip processing, real time hardware

acceleration, Profiling report showes less number of

execution cycles on PCLe based implementation.

Virtual servers with the help of openCL/C++

libraries, Xilinx SDx Environments and virtual JTAG

interfaces on Xilinx Virtex Ultrascale Plus

Board(VU9P) low profile PCIe accelerated Board

provides low latency and high performance software

profiling solutions.

REFERENCES

Jiapu Pan and Willis J. Tompkins, "A Real-Time QRS

Detection Algorithm" IEEE Transactions on

Biomedical Engineering, Vol. 32, No. 3, pp. 230-236,

March 1985.

Pratik D. Sherathia and V. P. Patel, "Fuzzy Inference

System based Detection of Wolff Parkinson's White

Syndrome, International Journal of Science,

Engineering and Technology Research, Vol. 6, Issue. 4,

pp. 660-664, April 2017.

Vijendra and Meghana Kulkarni, "Automatic ECG Signals

Recognition Based on Time Domain Features

Extraction Using Fiducial Mean Square Algorithm"

Springer Publications in Computational Intelligence:

Theories, Applications and Future Directions - Volume

I, Pages 18-94.

Shweta H. Jambukia, Vipul K. Dabhi and Harshadkumar B.

Prajapati, "Classification of ECG signals using

Machine Learning Techniques: A Survey, IEEE

International Conference on Advances in Computer

Engineering and Applications, pp. 714-721, India,

March 2015.

N. Bianchi, P. Bottoni, M. Cigada, A. De Giuli, P. Mussiol

and F. Sessa, Interpretation Strategies in a Cardiologist

Controllable Automatic Assistant for ECG Description

IEEE Proceedings of Computers in Cardiology, pp.

673-676, Italy, 1991.

Richard Mengko and Fredrick Sutjiady, Design and

Implementation of 12-Lead ECG Signals Interpretation

System, IEEE International Conference on Instrumen-

tation, Communications, Information Technology, and

Biomedical Engineering, pp. 278-282, Indonesia,

November 2013.

[Online]https://en.wikipedia.org/wiki/Butterworth.

Vijay Kr. Srivastava, Lalit Maurya and Er. Rajesh Mehra,

Detection of Noise in High Pass Butterworth IIR Filter

using MATLAB, International Journal of Engineering

Research & Technology, Vol. 3, Issue. 2, pp. 1232-

1235, February 2014.

Clifford E. Cummings, "Synthesis and scripting techniques

for designing multi asynchronous clock designs",

SNUG 2001.

Chris Spear, "System verilog for Verification, 2nd edition",

Springer, www.springeronline.com.

Benini, Roberto Zafalon, "Scalability analysis of evolving

Soc Interconnect protocols", International Symposium

on system on chip, 2004.

Lahir, K Raghunathan, "LOTTERYBUS: A new High

performance communication architecture for system on

chip" in Proceedings of Design Automation Conference

2001.

BIODEVICES 2019 - 12th International Conference on Biomedical Electronics and Devices

268